# **ComHeat Microwave**

- Comheat Microwave founded 2005 with main strategy to develop new high voltage devices in combination with CMOS and to support the transfer of these devices into production.

- Dr. Klas-Håkan Eklund

- Been in the industry for 50 years with main focus to develop high voltage devices in combination with CMOS.

- Jointly founded (Key founder) NASDAQ listed USD 500m company

- 20+ patents jointly or solely, related to Power Semiconductors.

- Dr. Lars Vestling

- Thesis: Design and modeling of high-frequency LDMOS transistors.

- Working 20 years in the industry mainly developing high-voltage silicon devices.

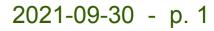

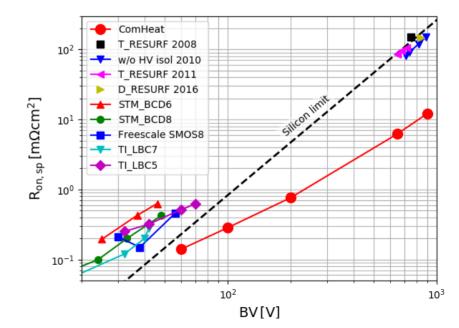

# New LDMOS - Status of the design

- LDMOS device design ready to be implemented in silicon

- Concept is competitive for voltages from 60V up to 900V.

- Product specifications and SPICE-models available.

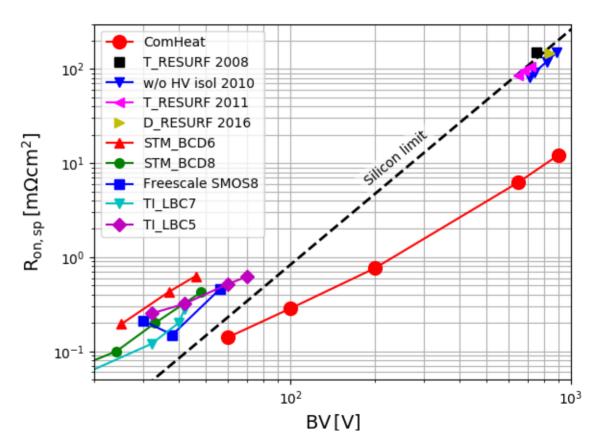

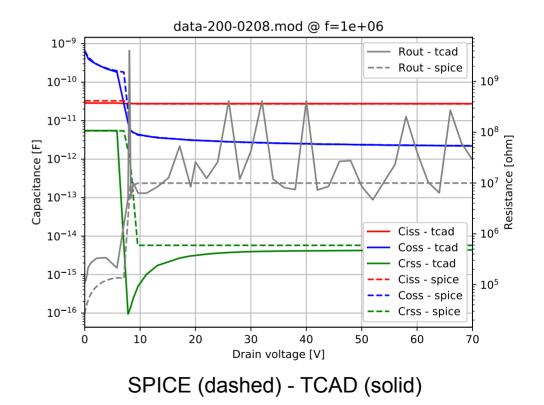

## Capacitance

- Capacitance comparison with similar discrete Si-device (Infineon CoolMOS).

- Miller capacitance (Crss) much lower.

| ME-L                                                                                              | DMOS I                                                | Power T     | ransiste | pr - 650V                                                           |  |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------|----------|---------------------------------------------------------------------|--|

|                                                                                                   | Con                                                   | Heat Mic    | owave    |                                                                     |  |

|                                                                                                   | N                                                     | vember 23.  | 0000     |                                                                     |  |

|                                                                                                   | NO                                                    | vember 23,  | 2020     |                                                                     |  |

| 1 Electrical charact<br>T <sub>j</sub> =25 °C unless otherwise spec<br>1.1 Maximum ratings        |                                                       |             |          |                                                                     |  |

| Parameter                                                                                         | Symbol                                                | Value       | Unit     | Test conditions                                                     |  |

| Gate voltage                                                                                      | VG                                                    | ±5          | V        | Test conditions                                                     |  |

| MOSFET dv/dt ruggedness                                                                           | $\frac{VG}{dv/dt}$                                    | ±0<br>50    | V/ns     |                                                                     |  |

| MOSTET uv/ut tuggetness                                                                           | ueyui                                                 | 00          | v/108    |                                                                     |  |

| 1.2 Static characteristic                                                                         | 5                                                     |             |          |                                                                     |  |

| Parameter                                                                                         | Symbol                                                | Value       | Unit     | Test conditions                                                     |  |

| On-resistance                                                                                     | R <sub>DS(on)</sub>                                   | 1.2         | 0        | $V_G=5 \text{ V}, I_D=1 \text{ A}, T_i=25 \text{ °C}$               |  |

|                                                                                                   | **DS(00)                                              | 2.0         |          | $V_G=5 V, I_D=1 A, T_i=125 ^{\circ}C$                               |  |

| Drain current                                                                                     | I <sub>D(sat)</sub>                                   | 3.2         | А        | $V_D=20 V, V_G=5 V$ , see fig. 1                                    |  |

| Zero gate voltage drain                                                                           | IDSS                                                  | <1          | μΑ       | $V_D = 600 \text{ V}, V_G = 0 \text{ V}, T_i = 25 ^{\circ}\text{C}$ |  |

| current                                                                                           | -000                                                  | <100        |          | $V_D = 600 \text{ V}, V_G = 0 \text{ V}, T_i = 125 \circ 0$         |  |

| Threshold voltage                                                                                 | $V_{GS(th)}$                                          | 0.46        | V        | $V_{GS}=V_{DS}, I_D=1 \text{ mA}, T_i=25 \circ C$                   |  |

| 0                                                                                                 | - 05(u)                                               | 0.46        | _        | $V_{GS}=V_{DS}, I_D=1 \text{ mA}, T_i=125^{\circ}$                  |  |

| Breakdown voltage                                                                                 | V <sub>br(off)</sub>                                  | >650        | V        | $V_G=0 V$                                                           |  |

| Pinch voltage                                                                                     | VP                                                    | 6.5         | V        | $V_G=0 V$                                                           |  |

| 1.3 Dynamic characteris<br>Parameter                                                              | Symbol                                                | Value       | Unit     | Test conditions                                                     |  |

| Input capacitance                                                                                 | Ciss                                                  | 73          | pF       |                                                                     |  |

| Output capacitance                                                                                | Coss                                                  | 4.2         | pF       | $V_G=0$ V, $V_D=100$ V, 1 MHz,                                      |  |

| Reverse transfer capacitance                                                                      | Cras                                                  | 0.001       | pF       | see fig. 2-3                                                        |  |

| Equivalent output<br>capacitance (energy related)                                                 | C <sub>o(er)</sub>                                    | 3.3         | pF       | $V_G=0$ V, $V_D=0$ V to 480 V                                       |  |

| Equivalent output                                                                                 | Co(tr)                                                | 37          | pF       | $V_G=0$ V, $V_D=0$ V to 480 V                                       |  |

| capacitance (time related)                                                                        |                                                       |             |          |                                                                     |  |

| Switching times for resisti                                                                       |                                                       |             |          |                                                                     |  |

|                                                                                                   | T <sub>d(on)</sub>                                    | 0.15        | ns       | $V_{DD}=300 \text{ V}, V_G=5 \text{ V}, R_L=150 \Omega$             |  |

| Turn-on delay time                                                                                | Trise                                                 | 3.1<br>4.2  | ns       |                                                                     |  |

| Rise time                                                                                         |                                                       |             | ns       |                                                                     |  |

| Rise time<br>Turn-off delay time                                                                  | $T_{d(off)}$                                          |             |          |                                                                     |  |

| Rise time<br>Turn-off delay time<br>Fall time                                                     | $T_{d(off)}$<br>$T_{fall}$                            | 4.2         | ns       |                                                                     |  |

| Rise time<br>Turn-off delay time<br>Fall time<br>Switching times for induct                       | $T_{d(off)}$<br>$T_{fall}$<br>ive load                | 3.7         |          |                                                                     |  |

| Rise time<br>Turn-off delay time<br>Fall time<br>Switching times for induct<br>Turn-on delay time | $T_{d(off)}$<br>$T_{fall}$<br>ive load<br>$T_{d(on)}$ | 3.7<br>0.15 | ns       | V                                                                   |  |

| Rise time<br>Turn-off delay time<br>Fall time<br>Switching times for induct                       | $T_{d(off)}$<br>$T_{fall}$<br>ive load                | 3.7         |          | $V_{DD}=300 \text{ V}, V_G=5 \text{ V}, I_D=1.0 \text{ A}$          |  |

### Electrical data comparison - 650V

|                    | ComHeat 650V<br>(LDMOS) | Si SJ (vertical)<br>IPZ65R095C7 | SiC (vertical)<br>C3M0060065D | GaN (lateral)<br>GS66504B |

|--------------------|-------------------------|---------------------------------|-------------------------------|---------------------------|

| R <sub>DS,on</sub> | 100mΩ                   | 100mΩ                           | 100mΩ                         | 100mΩ                     |

| $V_{GS(Th)}$       | 0.5V                    | 3.5V                            | 2.3V                          | 1.7V                      |

| C <sub>iss</sub>   | 730pF                   | 2000pF                          | 600pF                         | 120pF                     |

| C <sub>oss</sub>   | 42pF                    | 31pF                            | 90pF                          | 80pF                      |

| C <sub>rss</sub>   | 0.01pF                  | 2pF                             | 9pF                           | 0.8pF                     |

| Q <sub>g</sub>     | 7nC                     | 48nC                            | 28nC                          | 3nC                       |

All devices normalized to 100m $\Omega$ , capacitances at V<sub>G</sub>=0V, V<sub>D</sub>=100V

### Electrical data comparison – 200V

|                     | ComHeat 200V | Si-LDMOS<br>NXP MRFX1K80H |

|---------------------|--------------|---------------------------|

| R <sub>DS,on</sub>  | 80mΩ         | 80mΩ                      |

| V <sub>(BR)DS</sub> | 230V         | 193V                      |

| V <sub>GS(Th)</sub> | 0.5V         | 2.5V                      |

| C <sub>iss</sub>    | 380pF        | 760pF                     |

| C <sub>oss</sub>    | 25pF         | 203pF                     |

| C <sub>rss</sub>    | 0.04pF       | 2.9pF                     |

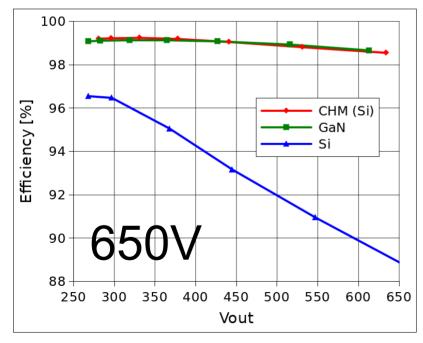

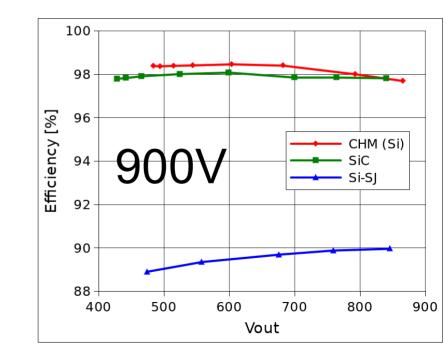

#### Comparison with GaN (650V) and SiC (900V)

- Boost converter, 1 MHz

- Vin = 250V and 400V

• SPICE-simulation

# SPICE model

- A compact model is developed and implemented in SPICE.

- Model parameters extracted from TCAD data.

- Plot shows comparison between TCAD (solid) and model (dashed).

## Manufacturing requirements

New LDMOS preliminary based on Silicon using strandard available equipment and processes used in semiconductor industry.

### Device costs

• Die size reduction by a factor 5 and higher yield means lower manufacturing cost and less expensive packaging.

## Functionality benefits

- Key capacitances will reduce with die size but especially the Miller capacitance has been further reduced to 1-10% which reduces power consumption, switching times but also increases reliability and robutness.

- Gate charge can be designed to be very low, partly due to lower gate voltages. Low gate charge is very important for efficient switching and simplifies gate drive design.

# System Integration

- Compability with CMOS even down to state-of-the-art with 1.8V gate drive logic and system integration on-chip.

- The device can be driven directly from CMOS. No need for an additional power supply.

- Actually, the concept can replace 3 devices with 1 device

- discrete power device, gate driver and CMOS logic